Intel386™ MicroComputer Model 302

Board Technical Reference Manual

intel

302

Intel386<sup>™</sup> MicroComputer Model 302 Board Technical Reference Manual

Order Number: 505067-002

Revision F

#### **WARNING**

This equipment has been tested with a Class B computing device and has been found to comply with the limits for a class B computing device, pursuant to subpart J of part 15 FCC rules. Only peripherals (computer input/output devices, terminals, printers, etc.) which comply with the class B limits may be attached to this computer product. Operation with non-compliant peripherals is likely to result in interference to radio and TV reception.

All cables used to connect to peripherals must be shielded and grounded. Operation with cables, connected to peripherals, which are not shielded and grounded may result in interference to radio and TV reception.

This equipment meets or exceeds requirements for safety in the US (UL 478 5th Edition), Canada (CSA C22.2 No. 220), and Europe (IEC 380, IEC 435, IEC 950, and VDE 0806).

This equipment has been tested for radio frequency emissions and has been verified to meet VDE 0871 Class B.

This digital apparatus does not exceed the Class B limits for radio noise emissions set out in the radio interference regulations of the Canadian Department of Communications.

Ce dispositif digital, s'il est utilise suivant les instructions et recommandations du constructeur, ne depasse pas les limites de la Classe B pour le bruit des frequences radio, etablies par les Regles sur l'interference radio du Ministere Canadian des Communications.

#### RADIO FREQUENCY INTERFERENCE NOTICE

This equipment generates and uses radio frequency energy and if not installed properly, that is, in strict accordance with the manufacturer's instructions, may cause interference to radio and television reception. It has been type-tested and found to comply with the limits for a Class B computing device in accordance with the specifications in Subpart J of Part 15 FCC rules, which are designed to provide reasonable protection against interference in a residential installation. However, there is no guarantee that interference will not occur in a particular installation. If the equipment does cause interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

- Reorient the receiving antenna.

- Relocate the system with respect to the receiver.

- Move the system away from the receiver.

- Plug the system into a different outlet so that the system and receiver are on different branch circuits.

- Move the cables connected to the system to minimize the interference.

- Tighten all screws on cables and the system housing.

- Install blank panels, originally supplied with the system, in all unused card slots.

If necessary the user should consult the dealer or an experienced radio/television technician for additional suggestions. The user may find the following booklet, prepared by the Federal Communications Commission, helpful:

"How to Identify and Resolve Radio-TV Interference Problems"

This booklet is available from the U.S. Government Printing Office, Washington, D.C. 20402. Stock No. 004-00398-5.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 58130 Santa Clara, CA 95052-8130

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software and firmware products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication, or disclosure is subject to restrictions stated in Intel's Software License Agreement, or in the case of software delivered to the U.S. government, in accordance with the software license agreement as defined in FAR 52.227-7013.

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

Intel Corporation retains the right to make changes to these specifications at any time, without notice. Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates, and may be used only to identify Intel products:

| Above         | iMDDX                  | iRMX            | Promware                |

|---------------|------------------------|-----------------|-------------------------|

| BITBUS        | iMMX                   | iSBC            | QueX                    |

| COMMputer     | Inboard                | iSBX            | QUEST                   |

| CREDIT        | Insite                 | iSDM            | Quick-Erase             |

| Data Pipeline | Intel®                 | iSXM            | Quick Pulse Programming |

| ETOX          | int <sub>e</sub> l®    | KEPROM          | Ripplemode              |

| Genius        | Intel376               | Library Manager | RMX/80                  |

| i486          | Intel386               | MAPNET          | RUPI                    |

| i860          | intelBOS               | MCS®            | Seamless                |

| ф             | Intel Certified        | Megachassis     | SLD                     |

| j®            | Intelevision           | MICROMAINFRAME  | SugarCube               |

| I2CE          | inteligent Identifier  | MULTIBUS        | UPI                     |

| ICE           | inteligent Programming | MULTICHANNEL    | VLSiCEL                 |

| iCEL          | Intellec®              | MULTIMODULE     | 376                     |

| ICEVIEW       | Intellink              | ONCE            | 386                     |

| iCS           | iOSP                   | OpenNET         | 386SX                   |

| iDBP          | iPAT                   | OTP             | 387                     |

| iDIS          | iPDS                   | PC BUBBLE       | 387SX                   |

| iLBX          | iPSC®                  | Plug-A-Bubble   | 4-SITE                  |

| im®           | iRMK                   | PROMPT          | 486                     |

MULTIBUS is a patented Intel bus.

IBM is a registered trademark of International Business Machines, Inc.

PC, XT, and AT are trademarks of International Business Machines, Inc.

Microsoft, MS-DOS, OS/2, and XENIX are registered trademarks of Microsoft Corporation.

Multiplan is a trademark of Microsoft Corporation.

UNIX is a trademark of AT&T.

Lotus 1-2-3 and Symphony are registered trademarks of Lotus Development Corporation.

Framework II and dBASE III PLUS are registered trademarks of Ashton-Tate.

MultiMate is a trademark of Ashton-Tate.

Centronics is a trademark of Centronics Data Computer Corporation.

Copyright © 1989,1990 Intel Corporation

| REV. | REVISION HISTORY             | DATE  |

|------|------------------------------|-------|

| -001 | Preliminary Release          | 11/89 |

| -002 | Original Issue (Release 1.0) | 1/90  |

### **Contents**

#### **About This Manual** Purpose ..... xxvii Library Plan ..... xxviii Audience..... xxviii Organization..... xxix How to Obtain More Information ..... xxxi Notational Conventions. xxxi Related Publications xxxiv 1 **Board Overview** 1.1 Introduction 1-1 1.2 Overview ..... 1-1 1.3 Feature Set Description..... 1-6 1.3.1 Central Processing Unit (CPU)..... 1-6 1.3.2 Memory ..... 1-6 1.3.3 AT32 Bus..... 1-6 1.3.4 Intel ISA Bus ..... 1-7 1.3.5 Programmable Interval Timer..... 1-7 1.3.6 Programmable Interrupt Controller ..... 1-7 1.3.7 DMA Controller 1-7 1.3.8 Real-time CMOS Clock 1-7 1.3.9 Input/Output Expansion Slots..... 1-8 Input/Output Ports..... 1.3.10 1-8 1.3.11 Keyboard Interface..... 1-8 1.3.12 Special Board Interfaces..... 1-8 1.3.13 Firmware ..... 1-9

| 2     | Central Processing Core                |      |

|-------|----------------------------------------|------|

| 2.1   | Introduction                           | 2-1  |

| 2.2   | Overview                               | 2-1  |

| 2.3   | CPU                                    | 2-3  |

| 2.3.1 | Real Mode Architecture                 | 2-3  |

| 2.3.2 | Protected Mode Architecture            | 2-3  |

| 2.3.3 | Virtual-8086 Mode                      | 2-4  |

| 2.3.4 | CPU Signals                            | 2-4  |

| 2.3.5 | Basic CPU Bus Operations               | 2-7  |

| 2.4   | Numeric Coprocessor                    | 2-10 |

| 2.4.1 | 387™ Numeric Coprocessor Data Types    | 2-10 |

| 2.4.2 | 387™ Coprocessor Programming Interface | 2-11 |

| 2.4.3 | Weitek 3167 Interface                  | 2-13 |

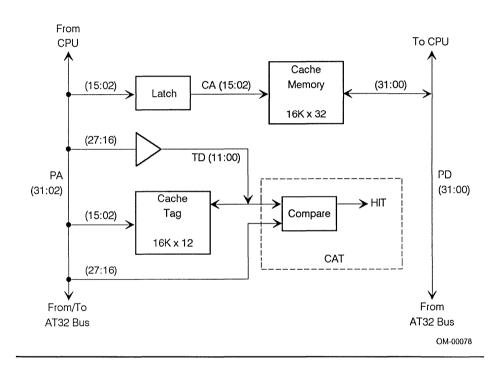

| 2.5   | Cache Memory and Tag                   | 2-14 |

| 2.5.1 | Cache Memory                           | 2-15 |

| 2.5.2 | Cache Tag Memory                       | 2-15 |

| 2.5.3 | Cache Memory Read Requests             | 2-15 |

| 2.5.4 | Cache Memory Write Requests            | 2-16 |

| 2.6   | Address and Data Buffers               | 2-16 |

| 2.7   | CPU/Cache Control                      | 2-16 |

| 3     | Onboard Memory                         |      |

| 3.1   | Introduction                           | 3-1  |

| 3.2   | Onboard Memory Overview                | 3-1  |

| 3.3   | 302 Board DRAM                         | 3-3  |

| 3.4   | Configuring AT32 Memory                | 3-4  |

| 3.5   | DRAM Refresh                           | 3-5  |

| 4     | Intel AT32 Bus Interface               |      |

| 4.1   | Introduction                           | 4-1  |

| 4.2   | AT32 Bus Overview                      | 4-1  |

| 5     | Intel ISA Bus                                                  |      |

|-------|----------------------------------------------------------------|------|

| 5.1   | Introduction                                                   | 5-1  |

| 5.2   | Bus Agents                                                     | 5-1  |

| 5.2.1 | Configuring Bus Agents                                         | 5-2  |

| 5.2.2 | Agent Functional Model                                         | 5-3  |

| 5.2.3 | General ISA Bus Attributes                                     | 5-4  |

| 5.3   | Signal Groups                                                  | 5-5  |

| 5.3.1 | Address Signal Group                                           | 5-6  |

| 5.3.2 | Data Signal Group                                              | 5-8  |

| 5.3.3 | Cycle Control Signal Group                                     | 5-9  |

| 5.3.4 | Central Control Signal Group                                   | 5-11 |

| 5.3.5 | Interrupt Signal Group                                         | 5-13 |

| 5.3.6 | Direct Memory Access Signal Group                              | 5-13 |

| 5.3.7 | Power Group                                                    | 5-14 |

| 6     | 8254 Programmable Interval Timer                               |      |

| 6.1   | Introduction                                                   | 6-1  |

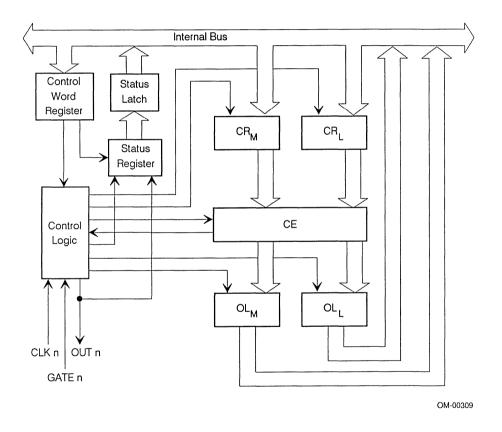

| 6.2   | Counter Description                                            | 6-2  |

| 6.2.1 | Control and Status Registers                                   | 6-4  |

| 6.2.2 | Counting Element (CE)                                          | 6-4  |

| 6.3   | Programming the PIT                                            | 6-5  |

| 6.3.1 | Control Register (043H)                                        | 6-5  |

|       | Read/Write Counter Command                                     | 6-7  |

|       | Latch-Counter Command                                          | 6-7  |

|       | Read-back Command                                              | 6-8  |

| 7     | 8259 Programmable Interrupt Controllers                        |      |

| 7.1   | Introduction                                                   | 7-1  |

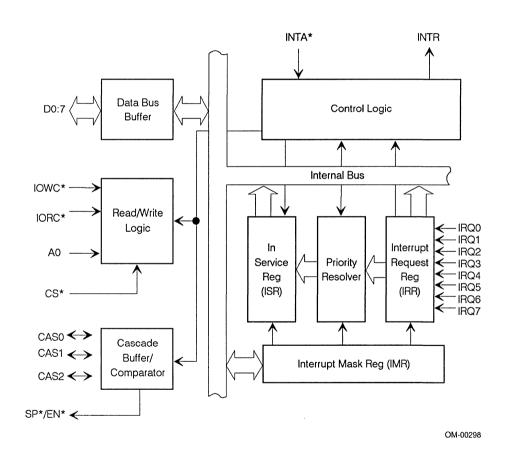

| 7.2   | Interrupt Controller Architecture                              | 7-4  |

| 7.2.1 | Interrupt Request Register (IRR) and In-service Register (ISR) | 7-4  |

| 7.2.2 | Interrupt Mask Register                                        | 7-4  |

| 7.2.3 | Priority Resolver                                              | 7-4  |

| 7.3   | Interrupts                                                     | 7-5  |

| 7.3.1 | Maskable Interrupts                                            | 7-5  |

| 7.3.2 | Non-maskable Interrupts                                        | 7-7  |

| 7     | 8259 Programmable Interrupt Controllers (continued) |      |

|-------|-----------------------------------------------------|------|

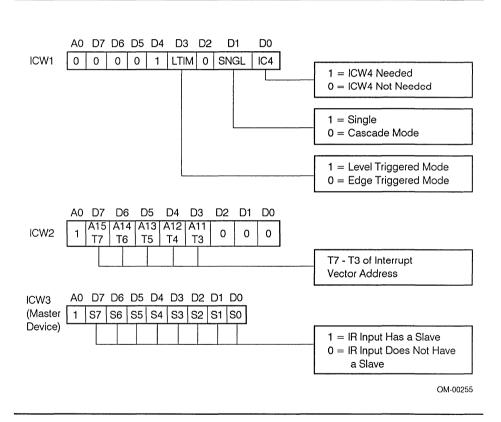

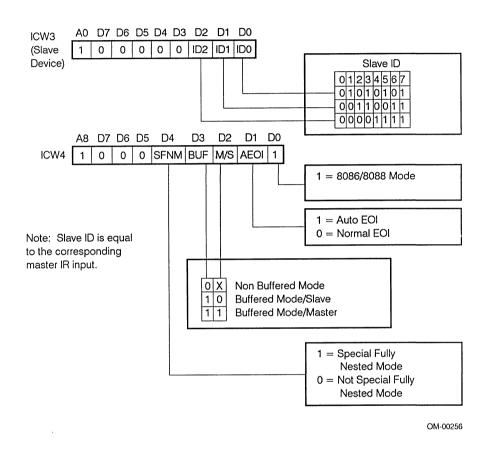

| 7.4   | Programming the PIC                                 | 7-8  |

| 7.4.1 | Initialization Command Word                         | 7-9  |

| 7.4.2 | Operational Command Word                            | 7-15 |

| 8     | Direct Memory Access (DMA)                          |      |

| 8.1   | Introduction                                        | 8-1  |

| 8.2   | DMA Operation                                       | 8-4  |

| 8.2.1 | Idle Cycle                                          | 8-4  |

| 8.2.2 | Active Cycle                                        | 8-4  |

|       | Single-Transfer Mode                                | 8-5  |

|       | Block-Transfer Mode                                 | 8-5  |

|       | Demand-Transfer Mode                                | 8-5  |

|       | Cascade Mode                                        | 8-6  |

| 8.3   | Transfer Types                                      | 8-6  |

| 8.4   | DMA Channels                                        | 8-7  |

| 8.5   | Programming The DMA Controllers                     | 8-8  |

| 8.6   | DMA Internal Registers                              | 8-9  |

| 8.6.1 | Address and Count Registers                         | 8-10 |

|       | Current Address Register                            | 8-11 |

|       | Current Word-Count Register                         | 8-11 |

|       | Base Address and Base Word-Count Registers          | 8-11 |

| 8.6.2 | Program-control Registers                           | 8-12 |

| 8.6.3 | Command Register                                    | 8-12 |

| 8.6.4 | Mode Register                                       | 8-14 |

| 8.6.5 | Request Register                                    | 8-15 |

| 8.6.6 | Mask Register                                       | 8-15 |

| 8.6.7 | Status Register                                     | 8-17 |

| 8.6.8 | Temporary Register                                  | 8-19 |

| 8.6.9 | Non-register Program Controls                       | 8-19 |

| 8.7   | Page Registers                                      | 8-20 |

| 9      | 1287 Real-time Clock (RTC)          |      |

|--------|-------------------------------------|------|

| 9.1    | Introduction                        | 9-1  |

| 9.2    | RTC RAM I/O Operations              | 9-1  |

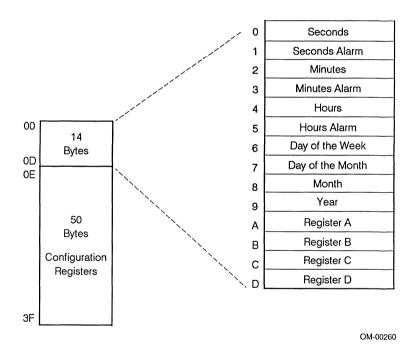

| 9.3    | RTC Addressable Locations           | 9-3  |

| 9.3.1  | Time, Calendar, and Alarm Bytes     | 9-5  |

| 9.4    | Status Registers                    | 9-7  |

| 9.4.1  | Status Register A                   | 9-7  |

| 9.4.2  | Status Register B                   | 9-8  |

| 9.4.3  | Status Register C                   | 9-10 |

| 9.4.4  | Status Register D                   | 9-11 |

| 9.5    | Configuration Bytes                 | 9-11 |

| 9.5.1  | Diagnostic Status Byte              | 9-12 |

| 9.5.2  | Shutdown Status Byte                | 9-13 |

| 9.5.3  | Floppy Disk Drive Type Byte         | 9-14 |

| 9.5.4  | Fixed Disk Drive Type Byte          | 9-15 |

| 9.5.5  | Equipment Byte                      | 9-16 |

| 9.5.6  | Low and High Base Memory Bytes      | 9-17 |

| 9.5.7  | Low and High Memory Expansion Bytes | 9-17 |

| 9.5.8  | Drive C Extended Byte               | 9-18 |

| 9.5.9  | Drive D Extended Byte               | 9-18 |

| 9.5.10 | Feature Installed Byte              | 9-18 |

| 9.5.11 | Fixed Disk Type 48 Parameters       | 9-19 |

| 9.5.12 | Shadow and Setup Byte               | 9-20 |

| 9.5.13 | CMOS RAM Checksum                   | 9-20 |

| 9.5.14 | Low and High Extended Memory Byte   | 9-21 |

| 9.5.15 | Date Century Byte                   | 9-21 |

| 9.5.16 | Setup Information Byte              | 9-22 |

| 9.5.17 | CPU Speed Byte                      | 9-22 |

| 9.5.18 | Fixed Disk Type 49 Parameters       | 9-23 |

| 10     | Communication Ports                 |      |

| 10.1   | Introduction                        | 10-1 |

| 10.2   | Serial Communication Ports          | 10-1 |

| 10.2.1 | CPU Interfacing                     | 10-2 |

| 10.2.2 | Connectors and Pinouts              | 10-2 |

| 10.3   | Parallel Printer Port               | 10-2 |

| 10.3.1 | Programming                         | 10-3 |

| 10.3.2 | Connector and Pinouts               | 10-5 |

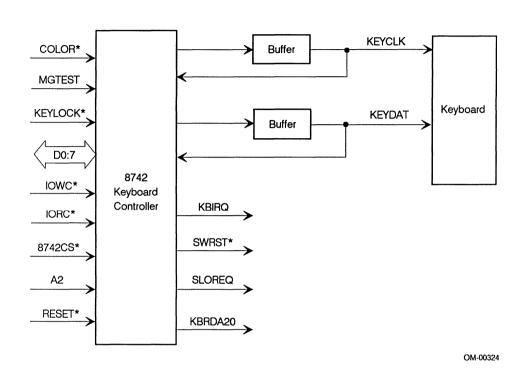

| 11     | Keyboard Controller                   |       |

|--------|---------------------------------------|-------|

| 11.1   | Introduction                          | 11-1  |

| 11.2   | Keyboard Controller System Interface  | 11-1  |

| 11.2.1 | Status Register                       | 11-3  |

| 11.2.2 | Output Buffer                         | 11-4  |

| 11.2.3 | Input Buffer                          | 11-4  |

| 11.2.4 | Input and Output Ports                | 11-5  |

| 11.3   | Controller Commands                   | 11-6  |

| 11.4   | Keyboard Interface                    | 11-7  |

| 11.4.1 | Keyboard Data Stream                  | 11-8  |

| 11.4.2 | Receiving Data from the Keyboard      | 11-9  |

| 11.4.3 | Sending Data to the Keyboard          | 11-11 |

| 11.5   | Keyclick Volume                       | 11-15 |

| 12     | 302 Board Special Interfaces          |       |

| 12.1   | Introduction                          | 12-1  |

| 12.2   | Keylock Interface                     | 12-1  |

| 12.3   | Speaker Interface                     | 12-2  |

| 12.4   | Reset Interface                       | 12-3  |

| 13     | Power-on Self Test and Setup          |       |

| 13.1   | Introduction                          | 13-1  |

| 13.2   | Power-on Self Test                    | 13-1  |

| 13.3   | Setup Program Overview                | 13-2  |

| 13.4   | Running The SETUP Program             | 13-3  |

| 13.4.1 | Moving Through Setup Screen 1         | 13-5  |

|        | Setting System Time                   | 13-5  |

|        | Setting System Date                   | 13-5  |

|        | Selecting Floppy disk Drive Types     | 13-6  |

|        | Setting Fixed disk Drive Types        | 13-6  |

|        | Setting Base Memory                   | 13-7  |

|        | Setting Extended Memory               | 13-7  |

|        | Setting Video Display Controller Type | 13-8  |

|        | Setting Keyboard Availability         | 13-9  |

|        | Setting CPU Speed                     | 13-9  |

|        | Numeric Coprocessor                   | 13-10 |

| 13     | Power-on Self Test and Setup (continued)             |       |

|--------|------------------------------------------------------|-------|

| 13.4.2 | Moving Through Setup Screen 2                        | 13-11 |

|        | Cache Memory                                         |       |

|        | AT32 I/O                                             |       |

|        |                                                      | 13-12 |

|        | 512-640 K                                            | 13-12 |

|        | Speaker                                              | 13-13 |

|        | Enter SETUP                                          | 13-13 |

| 13.5   | Exiting SETUP                                        |       |

| 13.6   | Error Messages                                       | 13-14 |

| A      | Specifications                                       |       |

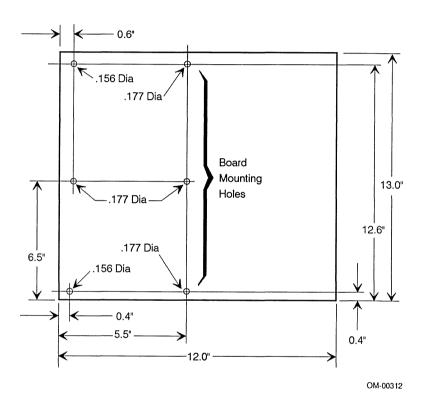

| A.1    | 302 Board Specifications                             | A-1   |

| A.2    | 302 Board Physical Characteristics                   | A-2   |

| A.3    | 302 Board Power Requirements                         | A-3   |

| В      | System BIOS Specifications                           |       |

| B.1    | Introduction                                         | B-1   |

| B.2    | Non-maskable Interrupt (INT 02H)                     | B-1   |

| B.3    | Print Screen (INT 05H)                               | B-2   |

| B.4    | System Timer H/W Interrupt (INT 08H)                 | B-2   |

| B.5    | Keyboard H/W Interrupt (INT 09H)                     | B-3   |

| B.6    | Disk H/W Interrupt (INT 0EH)                         | B-3   |

| B.7    | Video I/O (INT 10H)                                  | B-4   |

| B.7.1  | Set Display Mode                                     | B-5   |

| B.7.2  | Set Cursor Size                                      | B-6   |

| B.7.3  | Set Cursor Position                                  | B-6   |

| B.7.4  | Read Cursor Position                                 | B-7   |

| B.7.5  | Read Light Pen Position                              | B-7   |

| B.7.6  | Select Active Display Page                           | B-7   |

| B.7.7  | Scroll Window Up                                     | B-8   |

| B.7.8  | Scroll Window Down                                   | B-8   |

| B.7.9  | Read Attribute/Character at Current Cursor Position  | B-9   |

| B.7.10 | Write Attribute/Character at Current Cursor Position | B-9   |

| B.7.11 | Write Character Only at Current Cursor Position      | B-10  |

# B System BIOS Specifications (continued)

| B.7.12  | Set Color Palette                          | B-10 |

|---------|--------------------------------------------|------|

| B.7.13  | Write Dot                                  | B-11 |

| B.7.14  | Read Dot                                   | B-11 |

| B.7.15  | Write Character as Teletype to Active Page | B-11 |

| B.7.16  | Get Current Video Mode                     | B-12 |

| B.7.17  | Write String                               | B-12 |

| B.8     | Equipment Determination (INT 11H)          | B-13 |

| B.9     | Memory Size Determination (INT 12H)        | B-14 |

| B.10    | Floppy Disk Drive I/O (INT 13H, Part 1)    | B-14 |

| B.10.1  | Reset Disk Drive                           | B-15 |

| B.10.2  | Read Status                                | B-15 |

| B.10.3  | Disk Read                                  | B-16 |

| B.10.4  | Disk Write                                 | B-16 |

| B.10.5  | Disk Verify                                | B-17 |

| B.10.6  | Format Disk Track                          | B-17 |

| B.10.7  | Disk Drive Parameters                      | B-18 |

| B.10.8  | Read DASD Type                             | B-18 |

| B.10.9  | Disk Change Line Status                    | B-19 |

| B.10.10 | Set DASD Type for Format                   | B-19 |

| B.10.11 | Set Media Type for Format                  | B-20 |

| B.11    | Fixed Disk I/O (INT 13H, Part 2)           | B-21 |

| B.11.1  | Disk Reset                                 | B-22 |

| B.11.2  | Read Status                                | B-23 |

| B.11.3  | Read Disk                                  | B-23 |

| B.11.4  | Write Disk                                 | B-23 |

| B.11.5  | Verify Disk Sectors                        | B-24 |

| B.11.6  | Format Disk Track                          | B-24 |

| B.11.7  | Disk Drive Parameters                      | B-25 |

| B.11.8  | Initialize Disk Parameters                 | B-25 |

| B.11.9  | Disk Read Long                             | B-25 |

| B.11.10 | Disk Write Long                            | B-26 |

| B.11.11 | Disk Seek                                  | B-26 |

| B.11.12 | Disk Alternate Reset                       | B-27 |

| B.11.13 | Disk Ready Test                            | B-27 |

| B.11.14 | Disk Recalibrate                           | B-27 |

| B.11.15 | Disk Diagnostics                           | B-28 |

| B.11.16 | Read DASD Type                             | B-28 |

|         |                                            |      |

# B System BIOS Specifications (continued)

| B.12    | RS-232 I/O (INT 14H)                                       | B-29 |

|---------|------------------------------------------------------------|------|

| B.12.1  | Initialize the Communication Port                          | B-30 |

| B.12.2  | Send a Character                                           | B-31 |

| B.12.3  | Receive a Character                                        | B-32 |

| B.12.4  | Return the Communication Port Status                       | B-32 |

| B.13    | System Service Routines (INT 15H)                          | B-33 |

| B.13.1  | Keyboard Intercept                                         | B-34 |

| B.13.2  | Device Open                                                | B-35 |

| B.13.3  | Device Close                                               | B-35 |

| B.13.4  | Program Termination                                        | B-35 |

| B.13.5  | Event Wait                                                 | B-36 |

| B.13.6  | Joystick Support                                           | B-36 |

| B.13.7  | System Request Key Pressed                                 | B-37 |

| B.13.8  | Wait                                                       | B-37 |

| B.13.9  | Move Block                                                 | B-38 |

| B.13.10 | Extended Memory Size Determination                         | B-38 |

| B.13.11 | Switch CPU to Protected Mode                               | B-39 |

| B.13.12 | Device Busy                                                | B-39 |

| B.13.13 | Interrupt Complete                                         | B-40 |

| B.13.14 | Return System Configuration Parameters                     | B-40 |

| B.14    | Keyboard I/O (INT 16H)                                     | B-42 |

| B.14.1  | Read Next Character                                        | B-43 |

| B.14.2  | Read Buffer Status                                         | B-43 |

| B.14.3  | Return Shift Status                                        | B-44 |

| B.14.4  | Set Typematic Rate and Delay                               | B-45 |

| B.14.5  | Place ASCII Character/Scan Code in Keyboard Buffer         | B-46 |

| B.14.6  | Extended Read Interface for the Enhanced Keyboard          | B-46 |

| B.14.7  | Extended Buffer Status for the Enhanced Keyboard           | B-46 |

| B.14.8  | Return the Extended Shift Status for the Enhanced Keyboard | B-47 |

| B.15    | Printer I/O (INT 17H)                                      | B-48 |

| B.15.1  | Print Character                                            | B-48 |

| B.15.2  | Initialize Printer Port                                    | B-49 |

| B.15.3  | Read Printer Status                                        | B-49 |

| B.16    | System Boot (INT 19H)                                      | B-50 |

| В      | System BIOS Specifications (continued) |      |

|--------|----------------------------------------|------|

| B.17   | Clock Services (INT 1AH)               | B-50 |

| B.17.1 | Read the System Timer Count            | B-51 |

| B.17.2 | Set the System Timer Count             | B-51 |

| B.17.3 | Read the Real-time Clock Time          | B-51 |

| B.17.4 | Set the Real-time Clock Time           | B-52 |

| B.17.5 | Read the Real-time Clock Date          | B-52 |

| B.17.6 | Set the Real-time Clock Date           | B-53 |

| B.17.7 | Set the Real-time Clock Alarm          | B-53 |

| B.17.8 | Reset the Real-time Clock Alarm        | B-53 |

| B.18   | Real-Time Clock (INT 70H)              | B-54 |

| B.19   | Coprocessor Interrupt (INT 75H)        | B-54 |

| B.20   | Fixed Disk H/W Interrupt (INT 76H)     | B-54 |

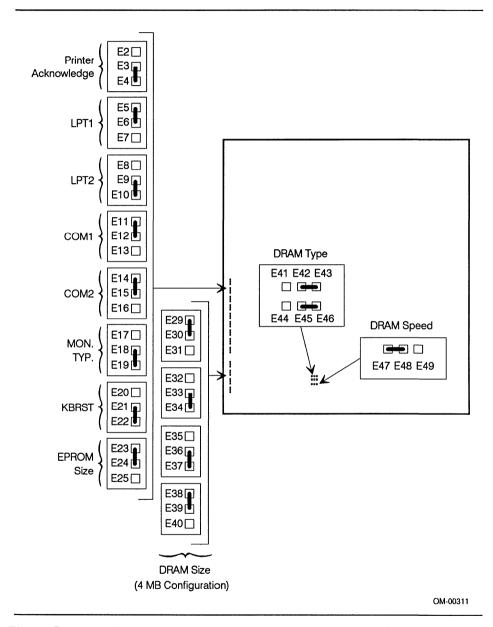

| C      | Jumper Settings                        |      |

| C.1    | Introduction                           | C-1  |

| C.2    | Total Onboard DRAM                     | C-3  |

| C.3    | Onboard ROM Size                       | C-3  |

| C.4    | Onboard RAM                            | C-4  |

| C.5    | Video Display Type                     | C-5  |

| C.6    | Printer Acknowledge                    | C-5  |

| C.7    | Parallel Printer Port Selection        | C-6  |

| C.8    | Serial Communications Port Selection   | C-6  |

| D      | Changing CPU Speed                     |      |

| D.1    | Introduction                           | D-1  |

| D.2    | Overview                               | D-1  |

| D.3    | Keyboard Method                        | D-2  |

| D.4    | Setup Method                           | D-2  |

| D.5    | Software Method                        | D-3  |

| E     | Messages                           |      |

|-------|------------------------------------|------|

| E.1   | Introduction                       | E-1  |

| E.2   | POST and Boot Messages             | E-1  |

| E.2.1 | POST and Boot Error Messages       | E-2  |

| E.2.2 | POST and Boot Information Messages | E-9  |

| E.3   | Run-Time Messages                  | E-11 |

| E.4   | 302 Board Errors                   | E-12 |

| F     | Device Mapping                     |      |

| F.1   | Introduction                       | F-1  |

| F.2   | System Memory Map                  | F-2  |

| F.3   | I/O Addresses                      | F-3  |

| F.4   | Interrupt Priority Levels          | F-7  |

| F.5   | DMA Channel Assignments            | F-8  |

| F.6   | RtC Mapping                        | F-8  |

| G     | Hot Keys                           |      |

| Н     | Pin Assignments for Major Signals  |      |

| H.1   | Introduction                       | H-1  |

| H.2   | CPU Pin Assignments                | H-1  |

| H.3   | AT32 Bus Pin Assignments           | H-3  |

| H.4   | ISA Bus Pin Assignments            | H-4  |

| H.5   | Serial Communications Port Pinouts | H-6  |

| H.6   | Parallel Printer Port Pinout       | H-8  |

| H.7   | Keyboard Pinout                    | H-9  |

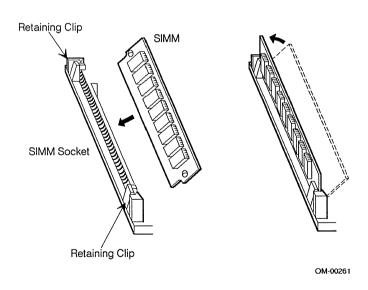

| I   | Installation                     |     |

|-----|----------------------------------|-----|

| l.1 | Introduction                     | I-1 |

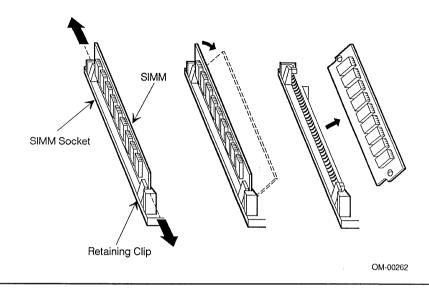

| 1.2 | Installing SIMMs                 | I-1 |

| 1.3 | Removing SIMMS                   | I-3 |

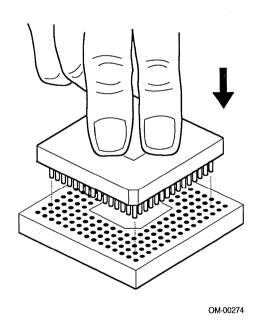

| 1.4 | Installing a Numeric Coprocessor | I-4 |

| l.5 | Removing a Numeric Coprocessor   | I-6 |

# Glossary

# Index

# int<sub>e</sub>l\* \_\_\_\_\_\_Figures

| 1   | Board Overview                                     |      |

|-----|----------------------------------------------------|------|

| 1-1 | 302 Board Component Layout                         | 1-3  |

| 1-2 | 302 Board Functional Block Diagram (sheet 1 of 2)  | 1-4  |

| 1-2 | 302 Board Functional Block Diagram (sheet 2 of 2)  | 1-5  |

| 2   | Central Processing Core                            |      |

| 2-1 | Central Processing Core                            | 2-2  |

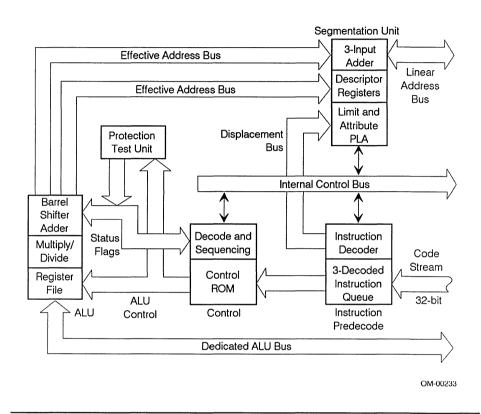

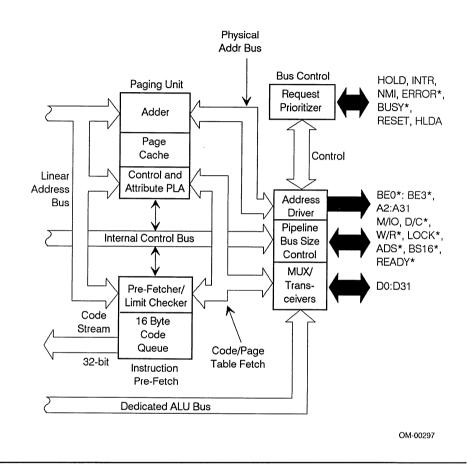

| 2-2 | CPU Block Diagram (sheet 1 of 2)                   | 2-8  |

| 2-2 | CPU Block Diagram (sheet 2 of 2)                   | 2-9  |

| 2-3 | Cache and Tag Memory                               | 2-14 |

| 6   | 8254 Programmable Interval Timer                   |      |

| 6-1 | Internal Block Diagram of a Counter                | 6-3  |

| 7   | 8259 Programmable Interrupt Controllers            |      |

| 7-1 | PIC Block Diagram                                  | 7-2  |

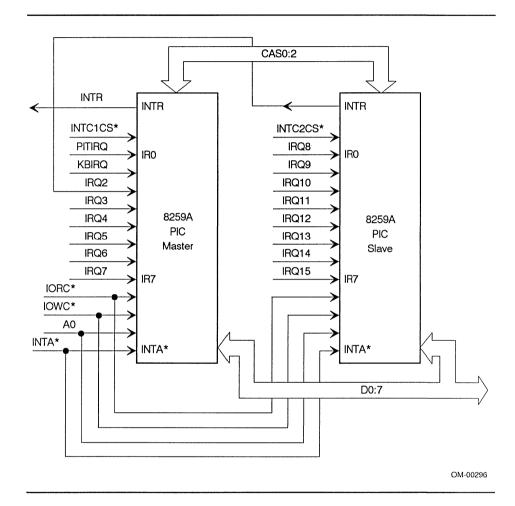

| 7-2 | Maskable Interrupt Logic                           | 7-3  |

| 7-3 | Command Word Format (ICW1, ICW2, and ICW3)         | 7-9  |

| 7-4 | Initialization Command Word Format (ICW3 and ICW4) | 7-10 |

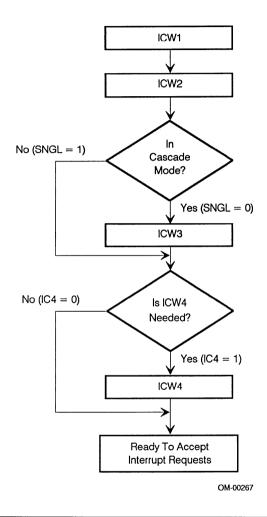

| 7-5 | Initialization Sequence Diagram                    | 7-11 |

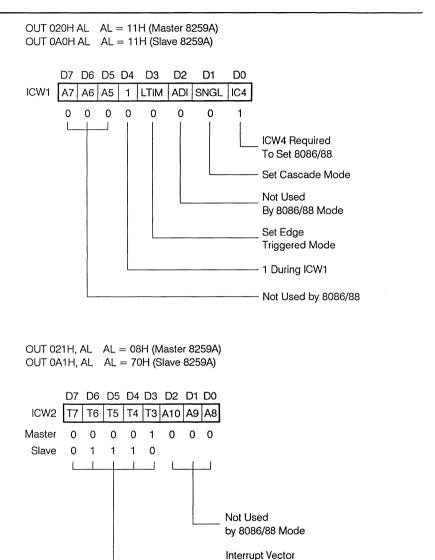

| 7-6 | Power-on Formats (ICW1 and ICW2)                   | 7-13 |

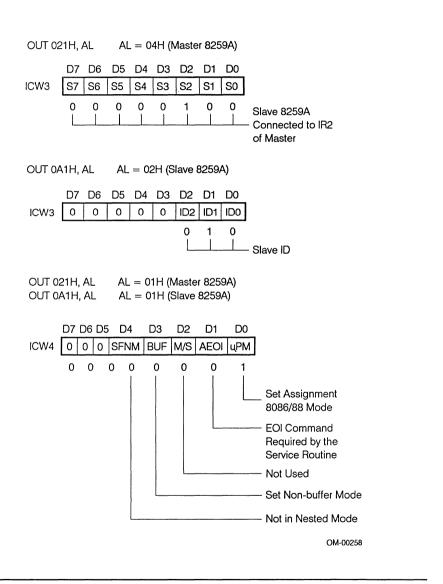

| 7-7 | Power-on Formats (ICW3 and ICW4)                   | 7-14 |

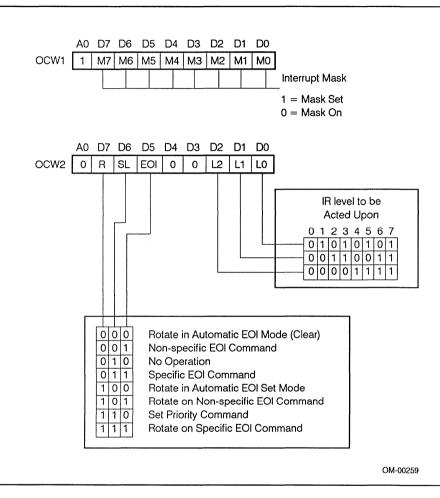

| 7-8 | Command Word Format (OCW1 and OCW2)                | 7-16 |

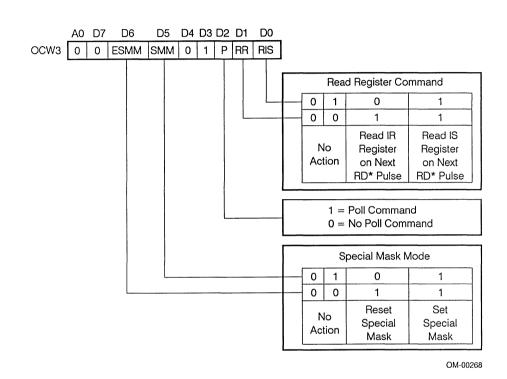

| 7-9 | Command Word Format (OCW3)                         | 7-17 |

|     |                                                    |      |

| 8                 | Direct Memory Access (DMA)                                     |                   |

|-------------------|----------------------------------------------------------------|-------------------|

| 8-1<br>8-2        | DMA Controller Block Diagram  DMA Logic                        | 8-2<br>8-3        |

| 9                 | 1287 Real-time Clock (RTC)                                     |                   |

| 9-1               | RTC Memory Map                                                 | 9-2               |

| 11                | Keyboard Controller                                            |                   |

| 11-1              | Keyboard Controller                                            | 11-2              |

| 13                | Power-on Self Test and Setup                                   |                   |

| 13-1<br>13-2      | Typical Setup Screen 1Typical Setup Screen 2                   | 13-4<br>13-10     |

| A                 | Specifications                                                 |                   |

| A-1               | 302 Board Dimensions                                           | A-2               |

| C                 | Jumper Settings                                                |                   |

| C-1               | 302 Board Jumper Locations                                     | C-2               |

| D                 | Changing CPU Speed                                             |                   |

| D-1<br>D-2        | Setting Deturbo Mode - Software Method                         | D-4<br>D-5        |

| I                 | Installation                                                   |                   |

| I-1<br>I-2<br>I-3 | Installing SIMMsRemoving SIMMsInstalling a Numeric Coprocessor | I-2<br>I-4<br>I-5 |

# **Tables**

| 3                               | Onboard Memory                                                                                                                                               |                                 |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 3-1<br>3-2<br>3-3<br>3-4        | Memory Address Map  Memory Resource Hierarchy  Memory Installed  Address Range                                                                               | 3-2<br>3-4<br>3-5<br>3-5        |

| 5                               | Intel ISA Bus                                                                                                                                                |                                 |

| 5-1<br>5-2                      | Number of Agents SupportedISA Bus Cycles                                                                                                                     | 5-2<br>5-3                      |

| 6                               | 8254 Programmable Interval Timer                                                                                                                             |                                 |

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5 | Counter Functions, Gates, and Signals  Counter/Timer Address Map  Control Register Bit Definition  Read-back Command Format  Format of a Latched Status Byte | 6-2<br>6-5<br>6-6<br>6-8<br>6-9 |

| 7                               | 8259 Programmable Interrupt Controllers                                                                                                                      |                                 |

| 7-1<br>7-2                      | Interrupt LevelsInterrupt Controller I/O Address and I/O Data                                                                                                | 7-6<br>7-8                      |

| 8    | Direct Memory Access (DMA)                             |      |

|------|--------------------------------------------------------|------|

| 8-1  | DMA Channel Assignment                                 | 8-7  |

| 8-2  | DMA Internal Registers                                 | 8-9  |

| 8-3  | I/O Port Addresses for DMA Address and Count Registers | 8-10 |

| 8-4  | Control Register I/O Port Addresses                    | 8-12 |

| 8-5  | Command Register Bit Assignments                       | 8-13 |

| 8-6  | Mode Register Bit Assignments                          | 8-14 |

| 8-7  | Request Register Update                                | 8-15 |

| 8-8  | Write Single Mask Bit Assignments                      | 8-16 |

| 8-9  | Write All Mask Bit Assignments                         | 8-17 |

| 8-10 | Status Register Bit Assignments                        | 8-18 |

| 8-11 | Lower-page Register Addresses for Each Channel         | 8-20 |

| 8-12 | Upper-page Register Addresses for Each Channel         | 8-21 |

| 9    | 1287 Real-time Clock (RTC)                             |      |

| 9-1  | Real-time Clock Address Map                            | 9-4  |

| 9-2  | Time, Calendar, and Alarm Data Format                  | 9-6  |

| 9-3  | Status Register A (0AH)                                | 9-7  |

| 9-4  | Status Register B (0BH)                                | 9-8  |

| 9-5  | Status Register C (0CH)                                | 9-10 |

| 9-6  | Status Register D (0DH)                                | 9-11 |

| 9-7  | Diagnostic Status Byte (0EH)                           | 9-12 |

| 9-8  | Shutdown Status Byte (0FH)                             | 9-13 |

| 9-9  | Floppy Disk Drive Type Byte (10H)                      | 9-14 |

| 9-10 | Fixed Disk Type Byte (12H)                             | 9-15 |

| 9-11 | Equipment Byte (14H)                                   | 9-16 |

| 9-12 | Low and High Base Memory Byte (15H and 16H)            | 9-17 |

| 9-13 | Low and High Memory Expansion Bytes (17H and 18H)      | 9-17 |

| 9-14 | Feature Installed Byte (1FH)                           | 9-18 |

| 9-15 | Fixed Disk Type 48 Parameters (20H:27H)                | 9-19 |

| 9-16 | Shadow and Setup Byte (28H)                            | 9-20 |

| 9-17 | Low and High Extended Memory Bytes (30H and 31H)       | 9-21 |

| 9-18 | Setup Information Byte (33H)                           | 9-22 |

| 9-19 | CPU Speed Byte (34H)                                   | 9-22 |

| 9-20 | Fixed Disk Type 49 Parameters (35H:3CH)                | 9-23 |

| 10   | Communication Ports                         |      |

|------|---------------------------------------------|------|

| 10-1 | Selection of Addresses and Interrupt Levels | 10-1 |

| 10-2 | Port Address and Interrupt Levels           | 10-3 |

| 10-3 | Input Instructions                          | 10-3 |

| 10-4 | Output Instructions                         | 10-4 |

| 10-5 | Parallel Port Registers (Bits 7-4)          | 10-4 |

| 10-6 | Parallel Port Registers (Bits 3-0)          | 10-5 |

| 11   | Keyboard Controller                         |      |

| 11-1 | Status Register Bit Assignments             | 11-3 |

| 11-2 | Input Port Bit Assignments                  | 11-5 |

| 11-3 | Output Port Bit Assignments                 | 11-6 |

| 11-4 | Controller Commands                         | 11-6 |

| 11-5 | Data Stream Bits                            | 11-8 |

| 12   | 302 Board Special Interfaces                |      |

| 12-1 | J23 Keylock Pinout                          | 12-1 |

| 12-2 | J23 Speaker Header Pinout                   | 12-2 |

| 12-3 | J23 Reset Interface Pinouts                 | 12-3 |

| A    | Specifications                              |      |

| A-1  | 302 Board Specifications                    | A-1  |

| A-2  | Physical Characteristics                    | A-3  |

| A-3  | Power Consumption                           | A-3  |

| A-4  | Maximum Current Ratings                     | A-4  |

| A-5  | Maximum +5V Current Drain on 302 Board      | A-5  |

| System BIOS Specifications                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video I/O Floppy Disk Drive I/O (part 1) Fixed Disk I/O (part 2) RS-232 I/O System Service Routines System Descriptor Table Gate A20 Control Routine Keyboard I/O Printer I/O Clock Services | B-4<br>B-14<br>B-21<br>B-29<br>B-33<br>B-41<br>B-41<br>B-42<br>B-48<br>B-50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Jumper Settings                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Total Onboard RAM Onboard ROM Size Onboard RAM Type Onboard RAM Speed Video Display Type Printer Acknowledge Parallel Printer Port Selection. Serial Communications Port Selection.          | C-3<br>C-4<br>C-4<br>C-5<br>C-5<br>C-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Messages                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Beep Codes for Fatal Errors  Beep Codes for Non-fatal Errors                                                                                                                                 | E-13<br>E-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Device Mapping                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Memory Address Map                                                                                                                                                                           | F-2<br>F-3<br>F-4<br>F-5<br>F-6<br>F-7<br>F-8<br>F-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                              | Video I/O Floppy Disk Drive I/O (part 1) Fixed Disk I/O (part 2) RS-232 I/O System Service Routines System Descriptor Table Gate A20 Control Routine Keyboard I/O Printer I/O Clock Services  Jumper Settings  Total Onboard RAM Onboard ROM Size Onboard RAM Speed Video Display Type Printer Acknowledge Parallel Printer Port Selection Serial Communications Port Selection  Messages  Beep Codes for Fatal Errors Beep Codes for Non-fatal Errors Beep Codes SMap I/O Address Map I/O Address Map I/O Address 79H Bit Assignments Interrupt Levels DMA Channel Assignment Interrupt Levels DMA Channel Assignment Interrupt Levels DMA Channel Assignment |

#### H Pin Assignments for Major Signals H-1 CPU Pin Assignments..... H-1 H-2 AT32 Bus Connector Pin Assignments..... H-3 H-3 ISA Bus 8-bit Connector Pin Assignments ..... H-4 H-4 ISA Bus 16-bit Connector Pin Assignments ..... H-5 H-5 Nine-pin Serial Port (COM1) Connector Pin Assignments ..... H-6 H-6 Nine-pin Serial Port (COM2) Connector Pin Assignments ...... H-6 H-7 25-pin Serial Port (COM2) Connector Pin Assignment..... H-7 H-8 Parallel Printer Port Connector Pin Assignments..... H-8 H-9 Keyboard Connector Pin Assignment ..... H-9

## **About This Manual**

#### **PURPOSE**

This manual provides reference data for the Intel386™ MicroComputer Model 302 Board. This gives system designers sufficient information to allow them to integrate the board into systems, and to test and evaluate that integration. System designers may also use this manual on a continuing basis to support their customers, solve problems, or expand the system. For example, this manual may be used to:

- Design or select system components such as expansion boards, peripheral devices, and replacement parts

- Select or design systems and applications software

- Solve system integration and interfacing problems

- Troubleshoot at an advanced level

- Program complex applications and systems software such as device drivers, interrupt handlers, etc.

#### LIBRARY PLAN

This manual is part of a set of three manuals written for the Intel386 MicroComputer Model 302 Board. A brief description of these manuals is as follows:

- Intel386™ MicroComputer Model 302 System Technical Reference Manual. This manual and its companion volume, Intel386™ MicroComputer Model 302 Board Technical Reference Manual, contain detailed technical information. The system manual focuses on the major elements contained in the system module chassis. It provides a general description of the system, a brief overview of the 302 board, all internal interfaces to other components, and all external interfaces. Basic installation and removal procedures for system components and peripheral devices are also included. A detailed description of the 302 board is contained in a separate manual (see following).

- Intel386™ MicroComputer Model 302 Board Technical Reference Manual.

This manual describes the 302 board in detail, and is written for engineers who design system accessories and for programmers who require information on hardware and firmware specifications.

- Intel386™ MicroComputer Model 302 System User's Guide. This manual is written for an end-user. It describes all system features, installation and operation of the system, how to install or remove system components, and basic troubleshooting procedures should problems occur.

#### **AUDIENCE**

This manual is written for an Original Equipment Manufacturer (OEM), or a system engineer or hardware or software designer. As such, it assumes you are familiar with the general terminology used in the field of microprocessor and microcomputer design.

# **ORGANIZATION**

This manual is organized as follows:

| Chapter 1  | Board Overview — provides an overview of the 302 board. Included is a list of features, a block diagram of the board and a description of the feature set.  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2  | Central Processing Core — describes the operation of the CPU, the 387 numeric coprocessor, cache memory, cache tag memory, and data and controller buffers. |

| Chapter 3  | Onboard Memory — describes the onboard dynamic random access memory (DRAM), single in-line memory modules (SIMMs), and 32-bit expansion board DRAM.         |

| Chapter 4  | Intel AT32 Bus Interface — provides a brief description of the AT32 Bus Interface.                                                                          |

| Chapter 5  | Intel ISA Bus — introduces the ISA bus, provides general attributes of the ISA bus, and describes the ISA bus signal groups.                                |

| Chapter 6  | 8254 Programmable Interval Timer (PIT) — describes the operation of the PIT.                                                                                |

| Chapter 7  | 8259 Programmable Interrupt Controllers (PICs) — describes the operation of the PICs.                                                                       |

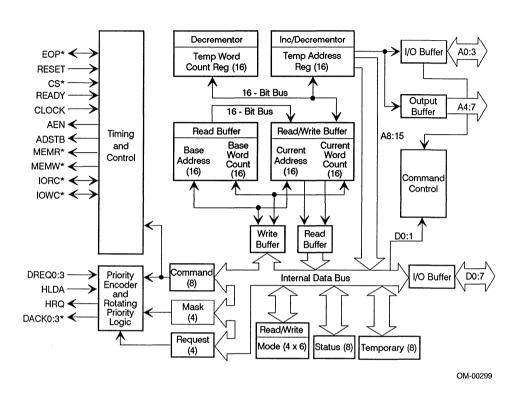

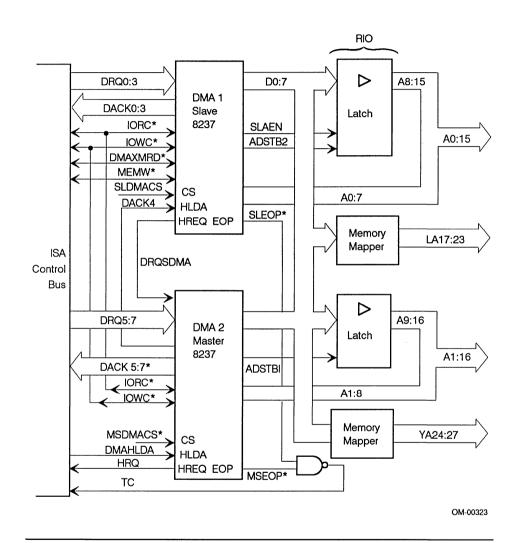

| Chapter 8  | Direct Memory Access (DMA) — describes the operation of the dual 8237 DMA controllers.                                                                      |

| Chapter 9  | 1287 Real-time Clock (RTC) — describes the operation of the RTC.                                                                                            |

| Chapter 10 | Communications Ports — describes the system serial and parallel communications ports.                                                                       |

| Chapter 11 | Keyboard Controller — describes the operation of the keyboard controller.                                                                                   |

Chapter 12 302 Board Special Interfaces — describes three special board interfaces: keylock, speaker, and the reset. Chapter 13 Power-on Self Test and Setup — describes the poweron self test and the setup utility stored in ROM. Appendix A Specifications — provides system specifications for the 302 board. Appendix B System BIOS Specifications — provides BIOS specifications for the 302 board. Jumper Settings — provides jumper settings for the 302 Appendix C board. Appendix D Changing CPU Speed — describes how to effectively reduce the processor clock speed to 8 MHz. Appendix E Messages — describes the various screen messages and error beep codes. Included are POST messages, run-time messages, board error messages, and beep codes. Device Mapping — provides tables that list mapping Appendix F and addressing information related to system memory and onboard devices. Appendix G Hot Keys — lists keystroke sequences used to invoke special system functions. Appendix H Pin Assignments for Major Signals — provides pin assignments for all major signals present in the 302 system. Appendix I Component Installation — describes how to install the Intel 387™ numeric coprocessor and SIMMs.

Glossary — defines the standard acronyms and

technical terms used in the field of microcomputer

design.

Index — provides important terms arranged in

alphabetical order for quick reference.

#### HOW TO OBTAIN MORE INFORMATION

You may be interested in obtaining further information about products and services relating to the Intel386 MicroComputer Model 302 Board. Or you may require more detailed information than is provided in this manual.

Please contact your local Intel Sales Office if you desire additional information.

#### NOTATIONAL CONVENTIONS

Certain notational conventions are used throughout this manual and others in the library. Refer to the glossary for specific definitions. Notational conventions include:

system Throughout this manual, the term "system" applies to the

Intel386™ MicroComputer Model 302 System.

board Throughout this manual, the term "302 board" or "board"

applies to the Intel386™ MicroComputer Model 302 Board.

A letter, number, symbol, or word enclosed in a double

rectangle, and printed in small type represents a a key on your

keyboard. For example, the instruction "press [1]" means

press the key labeled "F1" on your keyboard.

This manual refers to most keys by the symbol, letter, or name

printed on the key. The exception is the Backspace key. The

Backspace key is called Backspace to distinguish it from the left

arrow kev.

| Enter               | This manual uses Enter to refer to the two Enter keys. Other manuals refer to the Enter keys as RETURN, CARRIAGE RETURN, or use an arrow. All these items are interchangeable.                                                                                                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>x</b> + <b>y</b> | Two or three key names with plus signs between them indicate multiple-key entries. For example, TH + AH + DH means hold down the TH and AH keys and press the DH key.                                                                                                                                          |

| *                   | In signal definitions, the asterisk (*) following a signal name indicates an active low signal; for example IOCHCK*.                                                                                                                                                                                           |

| Н                   | An H suffix to a numerical value denotes hexadecimal numbers. For example, 0F8H means 0F8 (hexadecimal). See hex.                                                                                                                                                                                              |

| hex                 | Denotes hexadecimal numbers. Memory addresses are always listed in hexadecimal notation and are indicated by the term "hex" preceding or following the number; i.e., 0A hex or hex 8A. See H.                                                                                                                  |

| К                   | A K (upper case) suffix to a numerical value is used to indicate size in kilobytes; i.e., 7168K, 640K, etc. Note, that while a kilobyte is defined as 1024 bytes, the lower case k prefix used in other measurements indicates a quantity of 1,000. The K suffix is synonymous with KB or Kbyte. See Glossary. |

| Kb                  | A Kb suffix to a numerical value indicates size in kilobits. For example: 512Kb. (One kilobit is defined as 1024 bits.)                                                                                                                                                                                        |

| М                   | An M suffix to a numerical value is used to indicate size in megabytes; i.e., 1M, 256M, etc. Note, however, that while a megabyte is defined as 1,048,576 bytes the M prefix used in other measurements indicates a quantity of 1,000,000. The M suffix is synonymous with MB or megabyte. See Glossary.       |

| Mb                  | An Mb suffix to a numerical value indicates size in megabits. For example: 4Mb. (One megabit is defined as 1,048,576 bits.)                                                                                                                                                                                    |

All system messages (screen display) are shown in a non-proportional font to simulate the appearance of a screen display.

An italicized word or phrase is used to represent a variable, a publication title, or occasionally, to lend emphasis in textual descriptions. Where shown, DOS, UNIX or XENIX files, path names and directories are also italicized.

The longer POST and Boot error and informational messages in the index are followed by an ellipsis (three periods). This convention is used to denote that the message in the index is incomplete. The portion appearing in the index is of sufficient length to make a unique identification.

Four kinds of special notices are used throughout the text to emphasize specific information. Examples of each type of notice are as follows:

Notes are used to provide the reader with important or explanatory information that stands out from the rest of the text.

## **D** DANGER

DANGER indicates the presence of a hazard that will cause death or severe personal injury if the hazard is not avoided.

#### WARNING

WARNING indicates the presence of a hazard that can cause death or severe personal injury if the hazard is not avoided.

#### **CAUTION**

CAUTION indicates the presence of a hazard that can or will cause minor personal injury or damage to hardware or software.

, F

#### RELATED PUBLICATIONS

Refer to the following publications for additional information relating to the Intel386 MicroComputer Model 302 Board and its operating environment.

- Intel386™ MicroComputer Model 302 System Technical Reference Manual (Intel order number 505066-001)

- Intel386™ MicroComputer Model 302 User's Guide (Intel order number 505068-001)

- Introduction to the 80386 (Intel order number 231252-001)

- 80386 Programmer's Reference Manual (Intel order number 230985-001)

- 80387 Programmer's Reference Manual (Intel order number 231917-001)

- 386™ Microprocessor Hardware Reference Manual (Intel order number 231732-003)

- 80386 System Software Writer's Guide (Intel order number 231499-001)

- Microprocessor and Peripheral Handbook (Volume I and II) (Intel order number 230843-006)

## **Board Overview**

#### 1.1 INTRODUCTION

This chapter provides an overview of the 302 board. Included in this chapter is a list of features, a block diagram of the board, and a description of the feature set.

#### 1.2 OVERVIEW

The 302 board contains the following components:

- 25 MHz 386 central processing unit (CPU)

- 64K cache memory and cache tag memory

- ASIC device for CPU control logic (CAT)

- 1, 2, 4, or 8M of onboard memory

- 64K read-only memory (ROM)

- AT32 bus interface

- ASIC device for bus interface and memory control logic (DBC)

- Two direct memory access (DMA) controllers

- Two DMA page registers for accesses to memory throughout the full AT32 memory range.

- Two programmable interrupt controllers (PICs)

- Programmable interval timer (PIT)

- Real-time CMOS clock/calendar with integral lithium battery

- ASIC device for I/O decode logic (RIO)

- A 121-pin extended numeric coprocessor socket

- Eight I/O expansion slots (two 32-bit, five 16-bit, one 8-bit)

- I/O ports (two serial and one parallel)

- ROM-based setup program, BIOS, and power-on self test

- Keyboard controller and ports

- Reset interface

- Speaker interface

- Keylock interface

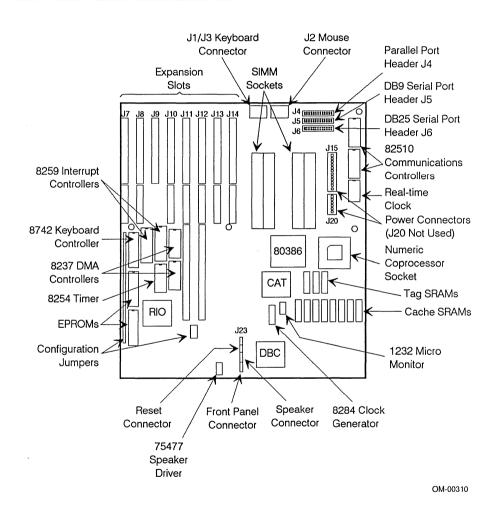

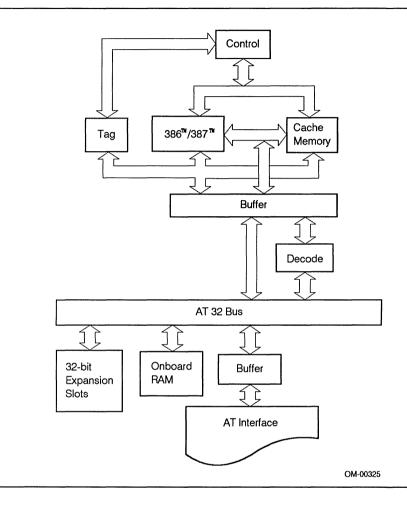

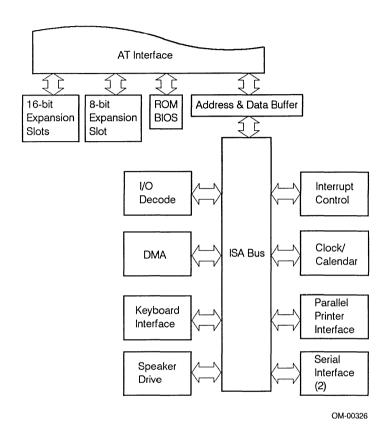

Figure 1-1 illustrates the component layout of the 302 board. Figure 1-2 shows a functional block diagram of the 302 board.

Figure 1-1. 302 Board Component Layout

Figure 1-2. 302 Board Functional Block Diagram (sheet 1 of 2)

Figure 1-2. 302 Board Functional Block Diagram (sheet 2 of 2)

#### 1.3 FEATURE SET DESCRIPTION

This section gives detailed description of the features listed earlier.

## 1.3.1 Central Processing Unit (CPU)

The CPU incorporates multitasking support, memory management, address translation caches, and a high-speed 32-bit bus interface. The CPU runs at a clock speed of 25 MHz resulting in a system speed of 40 ns per cycle. For applications requiring slower operation (such as installing some copy-protected software), a deturbo mode is provided. The deturbo mode reduces the effective system operating speed to 8 MHz by inserting wait states into the CPU cycle.

## 1.3.2 Memory

The 302 board contains three types of memory: read-only memory, cache and tag memory, and DRAM.

- The 302 board contains 64K of ROM. The ROM contains the BIOS, power-on self test (POST), and setup program.

- The 64K direct-mapped cache memory consists of eight static random access memory (SRAM) chips. The cache provides zero wait-state read performance and one wait-state write performance during CPU accesses. The tag memory consists of three SRAM chips and supplies 12-bit tag data for address comparison.

- The 302 board contains 4M (expandable to 8M) of DRAM.

#### 1.3.3 AT32 Bus

The AT32 bus supports 28-bit physical addresses and has a physical memory range of up to 256M. The AT32 bus is a high performance 32-bit extension to the Intel ISA bus. The AT32 bus provides a standard interface supporting additional memory, and I/O. The 302 board contains two AT32 slots, each capable of accepting 16M of DRAM.

#### 1.3.4 Intel ISA Bus

The system is compatible with the Intel ISA bus. I/O expansion boards communicate with the system via the ISA bus.

## 1.3.5 Programmable Interval Timer

Three general-purpose programmable interval timers (PITs), in an 82C54 integrated circuit, generate timing for memory refresh, software timing control, and speaker frequency generation.

## 1.3.6 Programmable Interrupt Controller

Two programmable interrupt controllers (PICs) provide 15 interrupt levels minimizing the software and real-time overhead in handling multilevel interrupts.

#### 1.3.7 DMA Controller

Two 8237 direct memory access (DMA) controllers provide seven DMA channels for data transfer between main memory and I/O devices. Each DMA controller generates the memory addresses and controls signals needed to transfer data.

## 1.3.8 Real-time CMOS Clock

The Real-time Clock (RTC) provides 50 bytes of CMOS RAM and a battery backup power source for keeping the system clock/calendar and system configuration parameters in nonvolatile memory. This protects the contents of both the RAM and the clock during system power-up and power-down.

## 1.3.9 Input/Output Expansion Slots

The system has eight I/O expansion slots:

- One slot (J9) accepts 8-bit expansion boards only.

- Five slots (J7, J8, J10, J13, and J14) accept 8-bit or 16-bit expansion boards.

- Two slots (J11 and J12) accept 8-, 16-, or 32-bit expansion boards that are compatible with the AT32 bus.

## 1.3.10 Input/Output Ports

The 302 board provides a parallel printer port configured as either LPT1 or LPT2, and two serial communications ports configured as COM1 and COM2. Both serial ports can be disabled by changing the jumper settings.

## 1.3.11 Keyboard Interface

The keyboard connects to the 302 board through a bidirectional synchronous serial port. The bidirectional serial interface converts signals and sends the data to and from a 101- or 102-key keyboard.

## 1.3.12 Special Board Interfaces

The 302 board incorporates three special interfaces: keylock, speaker, and reset.

#### **1.3.13** Firmware

The 302 board firmware consists of a POST that performs automatic system diagnostics, a setup program for setting system configuration parameters, and Phoenix Technologies' basic input/output system (BIOS).

The POST runs automatically and checks the CPU, keyboard, display, and system memory each time the system is turned on or rebooted.

The setup program is contained in the ROM BIOS on the 302 board and is used to store system configuration information. The information can be changed at any time by rerunning the setup program. The type of configuration information maintained by the setup program is as follows:

- Time and date

- Number and capacity of floppy disk drives

- Number and type of fixed disk drives

- Amount of base and extended memory

- Availability and type of primary display controller

- Keyboard present

- Coprocessor present

- CPU speed

- Shadow or do not shadow system BIOS and video BIOS

- Enable or disable cache memory, AT32 I/O, above 16M memory, speaker, and preboot SETUP

Onboard ROM consists of two 27256 EPROMS containing 64K of memory. The EPROMs contain the ROM code for the BIOS. Functions of the ROM BIOS are as follows:

- System initialization

- Power-on diagnostics

- System configuration

- Disk bootstrap loading

- Character bit patterns of the ASCII character set

- Storage of frequently needed input and output routines

If enabled in the setup program, the BIOS initializes the DRAM-shadowed BIOS option for increased system performance.

# **Central Processing Core**

#### 2.1 INTRODUCTION

This chapter describes the central processing core of the 302 board. The 386 CPU, the 387 numeric coprocessor, cache memory, cache tag memory, and address and data buffers are discussed. For more detailed information on these components, refer to the *Intel Microprocessor and Peripheral Handbook*.

#### 2.2 OVERVIEW

The central processing core contains the following components:

- A 386 32-bit CPU

- A 387 numeric coprocessor

- Cache memory

- Cache tag memory

- Address/data buffers

- An ASIC device for CPU and cache control (CAT)

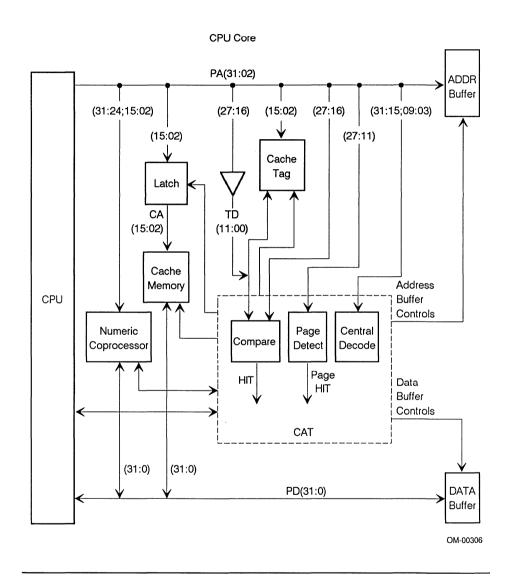

Figure 2-1 diagrams the central processing core.

Figure 2-1. Central Processing Core

#### 2.3 CPU

The CPU is a 386 microprocessor operating at 25 MHz. The CPU has separate 32-bit data and address paths, 32-bit registers, and on-chip memory management and protection. The CPU supports multiuser and multitasking systems, memory management, virtual memory, and task or memory isolation. Refer to "Related Publications" in About This Manual for a list of Intel reference manuals that provide detailed information on the 386 microprocessor.

#### 2.3.1 Real Mode Architecture

The CPU defaults to real mode upon reset. Real mode is compatible with 8086/8088 and 80286 CPUs at the object code level and has the same capabilities and limitations. In real mode addressable physical memory is limited to 1M via segment registers, with a 64K limitation on segment size. Real mode does not provide memory protection features.

Real mode addresses are formed, as in the 8086, by combining the base address from a segment register with the offset value provided by the instruction. The CPU shifts the 16-bit base address value in the segment register left four bits, and adds the 16-bit offset value forming the 20-bit real address.

### 2.3.2 Protected Mode Architecture

In protected mode, the CPU increases the linear address space to 4 gigabytes and lets the user run programs of almost unlimited size (up to 64 terabytes). In this mode, the integrated memory management and protection mechanism translates virtual addresses to physical addresses. Protected mode also isolates the operating system and enforces the protection rules that are necessary for maintaining task integrity in a multitasking environment. This is useful in a multitasking and multiuser environment where resources are shared.

Protected mode provides memory paging, I/O protection, virtual-8086 mode, and a full 32-bit extended instruction set. Protected mode also provides source-code compatibility with the 8086/8088 and 80286 CPUs. This allows the direct execution of 16-bit applications at higher speeds.

#### 2.3.3 Virtual-8086 Mode

The virtual-8086 mode is an extension of the protected mode. In this mode, the CPU provides compatibility with applications developed for the 8086/8088 while simultaneously providing a full 32-bit, large linear address programming environment in its protected mode.

Virtual memory allows programs to overcome the limitations of physical memory. The paging hardware allows the concurrent running of multiple virtual-8086 mode tasks and also provides protection and operating system isolation. The system divides virtual memory into many different segments which are mapped into physical memory during virtual memory execution. The memory management system transfers code and data between physical memory and disk memory.

## 2.3.4 CPU Signals

The following text defines the signal functions of the CPU. A signal name followed by an "I" in parentheses indicates an input signal, an "O" indicates an output signal and an "I/O" indicates an input/output signal. For more detailed information on the CPU signal functions, refer to the *Intel Microprocessor and Peripheral Handbook*.

| CLK2 (I)      | The CLK2 signal is a 50-MHz system clock signal. It provides the basic timing for the system. The CPU divides CLK2 by two to achieve a 25-MHz working clock.                      |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D(31:0) (I/O) | The D(31:0) signals are the data bus lines. These tristate bidirectional signals input data during memory and I/O read cycles and output data during memory and I/O write cycles. |

| A(31:2) (O)   | The A(31:2) signals are the address bus lines. These tristate signals output physical memory and I/O                                                                              |

addresses.

| BE(3:0)* (O) | The BE(3:0)* signals are the byte enables. These signals indicate which bytes of the data lines will carry data for the current transfer.                                                                                                                                             |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADS* (O)     | The ADS* signal is the address status. When ADS* is asserted, it indicates the beginning of a bus cycle. While ADS* is asserted, address lines A(31:2) are valid.                                                                                                                     |  |

| M/IO* (O)    | The M/IO (memory or I/O) signal indicates whether the access is to memory or an I/O device. When asserted (high), M/IO indicates that a memory or halt/shutdown cycle is in progress. When deasserted (low), M/IO indicates that a I/O or interrupt-acknowledge cycle is in progress. |  |

| D/C* (O)     | The D/C (data/control) signal is dual-purpose. When asserted (high), D/C indicates that a data cycle is in progress. When deasserted (low), D/C indicates that a control cycle is in progress.                                                                                        |  |

| W/R* (O)     | The W/R (write/read) signal is dual-purpose. When asserted (high), W/R indicates that a write cycle is in progress. When deasserted (low), W/R indicates that a read cycle is in progress.                                                                                            |  |

| LOCK* (O)    | The LOCK* signal, when asserted, indicates a locked bus. It prevents access by an external coprocessor until the CPU completes a read or modifying a byte in memory.                                                                                                                  |  |

| READY* (I)   | The READY* signal, when asserted, indicates the termination of a bus cycle and that the bus is available. Bus cycles are extended until terminated.                                                                                                                                   |  |

| HOLD (I)     | The HOLD signal is the bus hold request. The signal requests ownership of the CPU local bus.                                                                                                                                                                                          |  |